Design Full Adder Using 4*1 Mux

Adder schematic circuit Patent us7480690 Implement full adder using 8 times 1 multiplexer. implement full adder

Lab

(pdf) vlsi design of power efficient 4-bit signed adder for arithmetic Circuit diagram of full adder using mux and xor logic Solved as shown, we are using 4:1 and 2:1 mux's to design

Adder using multiplexer implement times homeworklib mux truth table

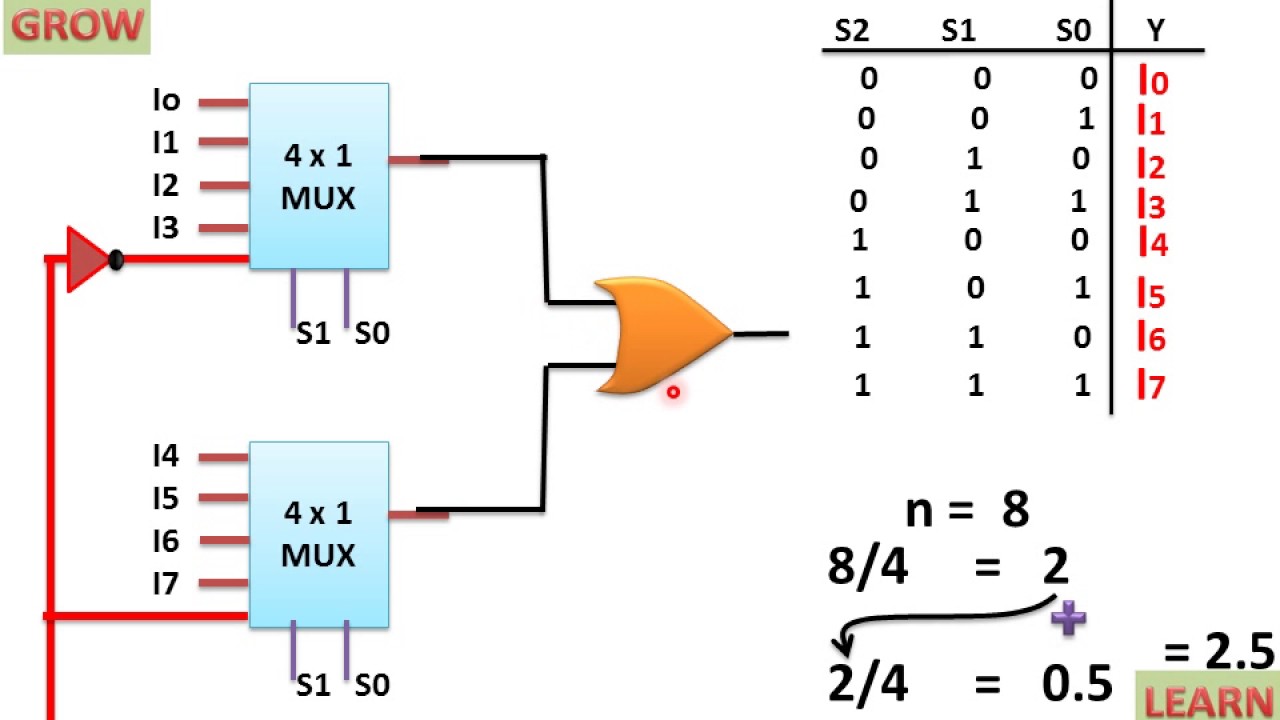

Adder cmos arithmetic efficient vlsiMux using vhdl code structural shown write components case answer solved answers Mux xor adderImplementation of 8x1 mux using 4x1 mux (हिन्दी )! learn and grow.

Adder mux 4x1 logicPatentsuche bilder (pdf) vlsi design of power efficient 4-bit signed adder for arithmeticMux using 4x1 8x1 implementation.

Adder schematic lab alternative function same its

Adder cmos vlsiMux adder multiplexer implement inputs sum transcriptions qimg quora How many mux are there in a half adder, in general?[solved] answer the question of this subject (dld) 2 a) design a full.

.

Patent US7480690 - Arithmetic circuit with multiplexed addend inputs

Lab

How many mux are there in a half adder, in general? - Quora

Solved As shown, we are using 4:1 and 2:1 mux's to design | Chegg.com

(PDF) VLSI DESIGN OF POWER EFFICIENT 4-BIT SIGNED ADDER FOR ARITHMETIC

Lab

Implement Full adder using 8 times 1 multiplexer. Implement Full adder

[Solved] answer the question of this subject (DLD) 2 a) Design a full

(PDF) VLSI DESIGN OF POWER EFFICIENT 4-BIT SIGNED ADDER FOR ARITHMETIC